LAPORAN PERCOBAAN 3

[KEMBALI KE MENU SEBELUMNYA]

1. Jurnal [Kembali]

Percobaan 3

-PERCOBAAN A

2. Alat dan Bahan [Kembali]

3. Rangkaian [Kembali]

4. Prinsip Kerja [Kembali]

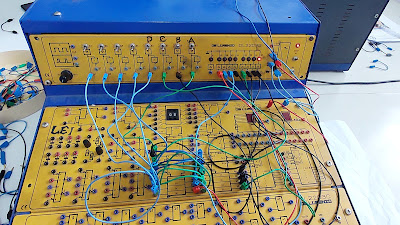

Pada percobaan 3A, percobaan ini menggunakan IC 74193 dan IC 74192, dan disini terdapat 8 buah switch dan ada 4 buah switch yang di variasikan yaitu S0 S1 S2 S3, dimana S0 sendiri itu dr, S1 adalah up, S2 merupakan down, dan S3 itu load. Inputan untuk IC itu ada D0 D1 D2 D3, kita bisa juga memvariasikan data2 nya, jika diberikan clock pada up maka akan menghasilkan counter up pada kedua output IC nya, begitu pun untuk down, jika diberikan clock pada down nya, maka akan menghasilkan kedua outputnya counter down. lalu MR pada IC sendiri merupakan master reset, fungsinya untuk mereset hasil perhitungan. Lalu pada IC terdapat Q0, Q1, Q2, dan Q3, dimana itu output dari IC sendiri. D0, D1, D2, D3 itu bisa juga divariasikan jika D0 yang dihidupkan maka Q0 akan aktif, dan jika D1 dihidupkan maka Q1 akan aktif. pada percobaan ini saya coba mengambil kondisi 4 dimana, S0 nya di nonaktifkan dan S1 atau bisa di sebut sebagai up diberikan clock dan S2 atau down diaktifkan atau berlogika 1, selanjutnya S3 atau load di beri logika satu, dimana hasil output dari kondisi ini adalah counter up di kedua bagian IC, karena disini clock terhubung kepada up.

-PERCOBAAN A

-PERCOBAAN B

Soal analisa yang diberikan ada 3 yakni:

1. Analisa output percobaan berdasarkan IC yang digunakan

jawab:

Pada percobaan 3A IC yang digunakan adalah IC 74193 dan IC 72192 dimana pada percobaan ini sama sama merupakan IC counter sinkron, yang membedakan IC tersebut adalah prinsip kerja di dalam IC iC tersebut. Kedua IC memiliki output yang sinkron dengan inputannya kedua IC

2. Analisa hasil percobaan pada kondisi 3 dan 4 !

jawab:

Pada percobaan 3A kondisi 3 terdapat switch S0, S1, S2, S3 dimana S0 sendiri clr S1 itu up, S2 merupakan down, dan S3 itu load, disini semua switch tidak di aktifkan dan menghasilkan output kiri on bukan counter dan output kanannya on bukan counter. Sedangkan kondisi 4 untuk loadnya aktif dan downnya aktif sedangkan kondisinya counter up berarti output kanannya counter up dan output kirinya pun counter uo karena clocknya berada di up

3. Apa pengaruh gerbang OR pada rangkaian

jawab:

Jika salah satu switch dari S1 dan S2 berbeda logikannyya, maka dia akan mengikuti kaki yang berlogika 1 namun jika keduanya sama sama bernilai 1 dan o maka clock tidak akan berfungsi pada output atau output menjadi diam / tetap

.jpeg)

.jpg)

Tidak ada komentar:

Posting Komentar